What is ISSIE

Interactive Schematic Simulator and Integrated Editor (ISSIE) is a very easy to use application for digital circuit design and simulation. It is targeted at students and hobbyists that want to get a grasp of Digital Electronics concepts in a simple and fun way. Issie is designed to be beginner-friendly and guide the users toward their goals via clear error messages and visual clues. Issie is developed and actively used in teaching at Imperial College London.

Issie has been well tested on designs with up to 15,000 schematic components. We expect it to be reasonably performant on much larger designs as well. The simulation speed is approximately 2000 component-clocks per ms. Thus a circuit with 1000 components would run at 2000 clocks per second. Issie creates fully synchronous circuits with a single clock: logic with asynchronous loops is currently not supported.

The application is mostly written in F#, which gets transpiled to JavaScript via the Fable compiler. Electron is then used to convert the developed web-app to a cross-platform application.

Key Features

Component Library

Viewer components are used to (optionally) view simulation waveforms of nodes on subsheets. Wire label components allow any number of nodes on one design sheet to be connected without visible wires.

Under ‘THIS PROJECT’ you can find all other design sheets of your project as custom components which can be added to your current sheet and replicate the sheet logic.

Wire Routing

Wires will all start out as Auto-routed, which means that the wire’s path is created automatically by the program. This path will update when moving any connected components. ISSIE also allows for manual routing, where the user may manipulate segments of the wire as desired to make the circuit more readable.

Canvas Customisation

(a) Rotate, Flip and Move around all symbols

(b) Change and Move around the symbols’ labels

(c) Manually route wires as you like

(d) Auto-align elements

(e) Select the wire type you desire (radiussed, jump or modern wires)

Width Inference

Step Simulation

Waveform Simulation

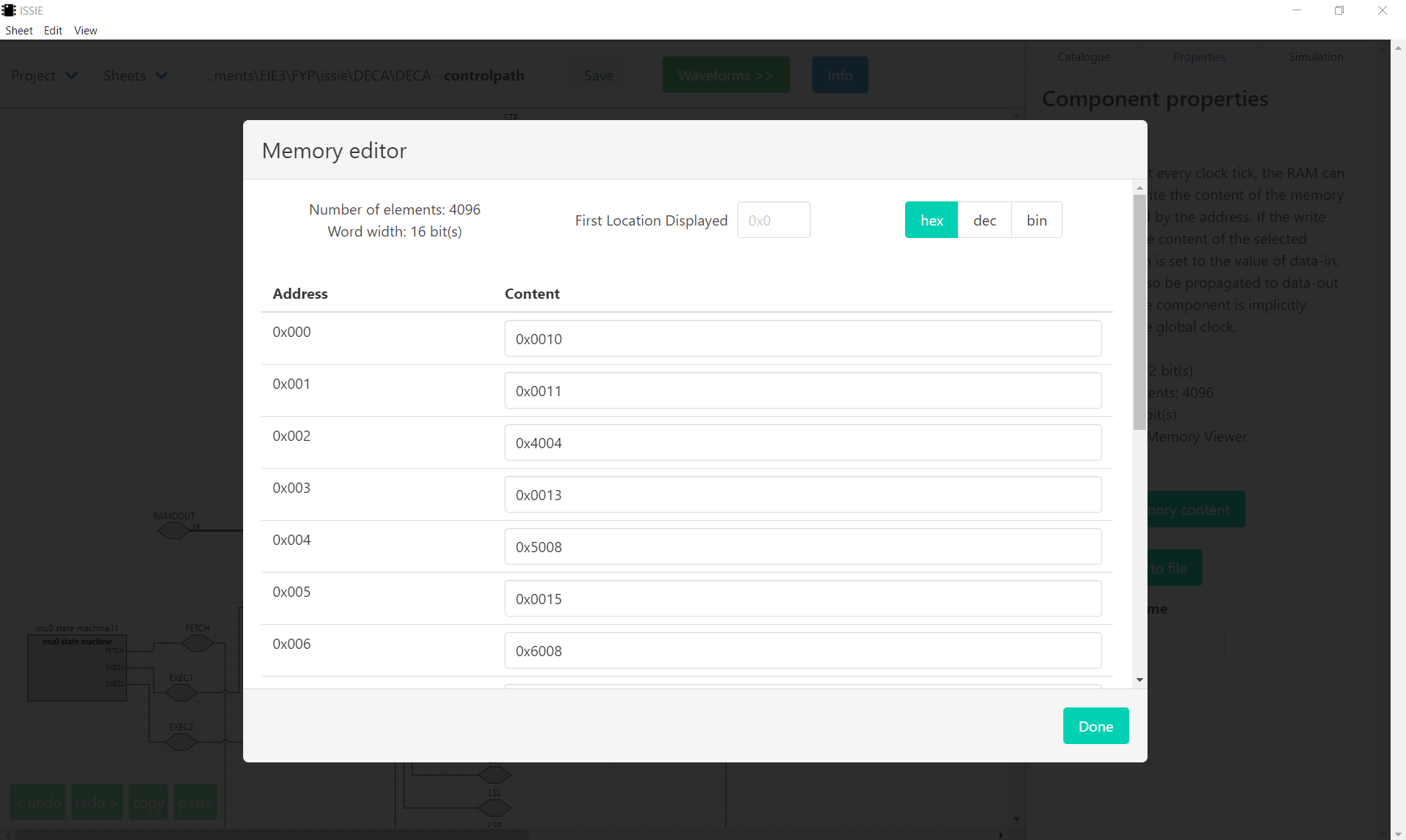

Waveform Simulation also allows for the simulation and contents viewing of memory components such as RAM.

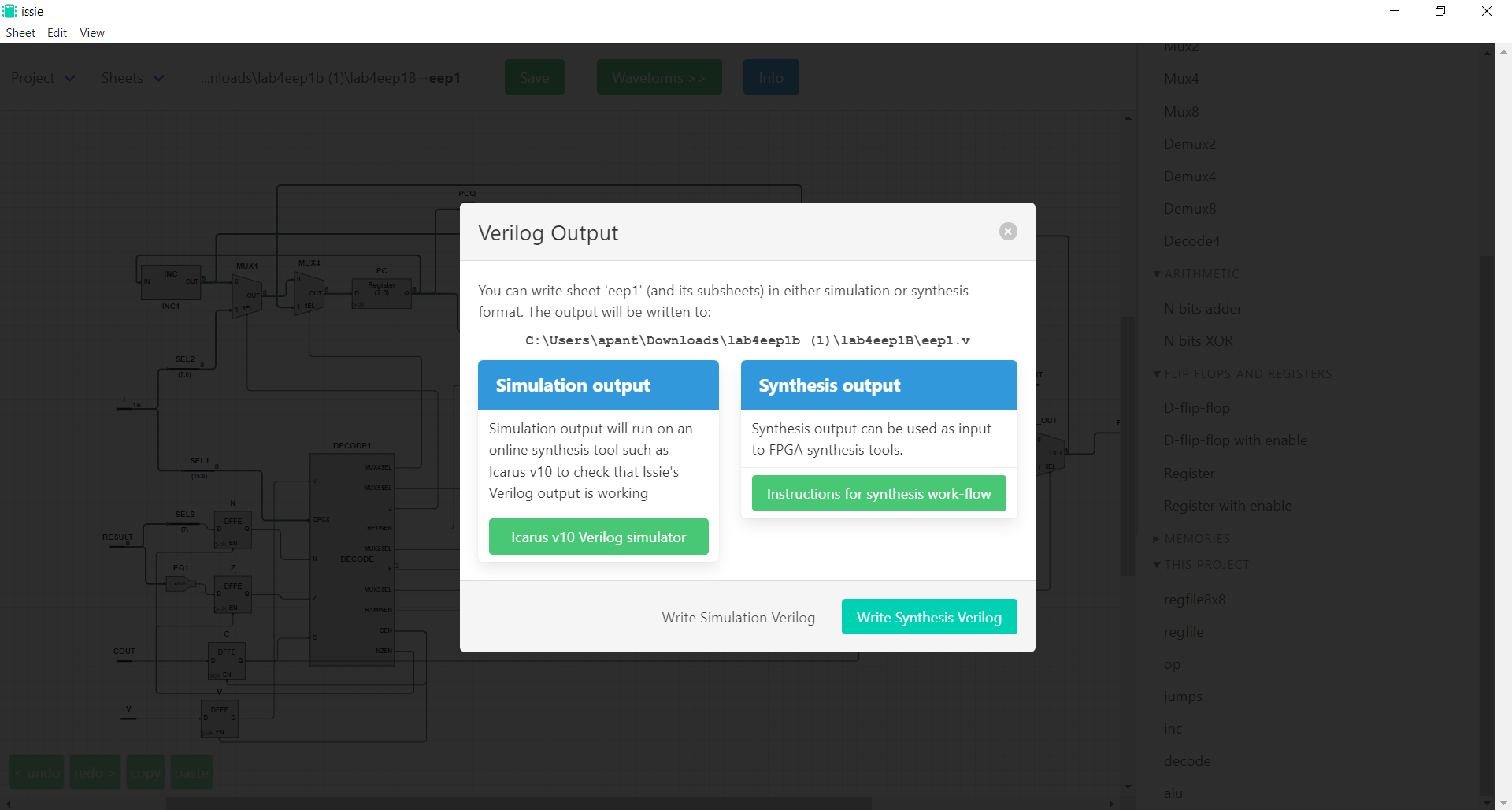

Verilog Output

Memory Editor

Acknowledgements

- Marco Selvatici for the 8K lines of base code written for his 3rd year BEng FYP

- Edoardo Santi for work improving Issie over Summer 2020.

- High Level Programming 2020 cohort for providing the base code of the draw block

- Jo Merrick for work improving ISSIE for her 3rd year BEng Project

- Dr Tom Clarke for his continued work maintaining and improving ISSIE throughout

- All 2020/2021 1st year undergraduate students of the EEE department, Imperial College London, for acting as unpaid beta-testers!

Contact

If you encounter any problems using or downloading the software, please see the Gihub Issue page, or create a new issue on the ISSIE GitHub repository. Any feedback and suggestions are also welcome!